“Esp32 spec”的版本间的差异

来自个人维基

free6d1823(讨论 | 贡献) |

free6d1823(讨论 | 贡献) |

||

| (未显示1个用户的4个中间版本) | |||

| 第57行: | 第57行: | ||

BT | BT | ||

WIFI | WIFI | ||

| + | |||

| + | Peripharels: 41 device | ||

| + | control registers 0x3FF0_0000~ 0x3FF7_FFFF, each device use 4KB space. | ||

| + | 系统中有两个PID Controller 分别服务于PRO_CPU 和APP_CPU。 | ||

| + | CPU 不能访问对方的PID Controller | ||

| + | |||

| + | Interrupt: | ||

| + | 71 external sources: 71 个外部中断源中有67 个可以分配给两个CPU。其余的4 个外部中断源只能分配给特定的CPU,每个CPU 2 个。 | ||

| + | 26 interrupt source for each core. | ||

| + | each CPU has 32x interrupt, include 26x external interrupt. | ||

| + | internal interrupt: (6/7/11/15/16/29) | ||

| + | timer0/1/2, software, | ||

| + | |||

| + | Reset: | ||

| + | COU reset: 只复位CPU 的所有寄存器。(CPU) | ||

| + | Core reset: 除了RTC,会把整个digital 的寄存器全部复位,包括CPU、所有外设和数字GPIO。 (CPU+WIFI+BT+PERI+Digital GPIO) | ||

| + | system rest: 会复位整个芯片所有的寄存器,包括RTC (PMG+Sensor+ULP+RTC GPIO)。 | ||

| + | |||

| + | Clock sources: | ||

| + | • 快速时钟 | ||

| + | – PLL_CLK,320 MHz 内部PLL 时钟 | ||

| + | – XTL_CLK,2 ~ 40 MHz 外部晶振时钟 | ||

| + | • 低功耗慢速时钟 | ||

| + | – XTL32K_CLK,32 KHz 外部晶振时钟 | ||

| + | – RTC8M_CLK,8 MHz 内部时钟,频率可调 | ||

| + | – RTC8M_D256_CLK 由RTC8M_CLK 256 分频所得,频率为(RTC8M_CLK 256)。当RTC8M_CLK 的初始频率为8 MHz 时,该时钟以31.250 KHz 的频率运行。 | ||

| + | – RTC_CLK,150 KHz 内部低功耗时钟,频率可调 | ||

| + | • 音频时钟 | ||

| + | – APLL_CLK,16 ~ 128 MHz 内部Audio PLL 时钟 | ||

| + | [[文件:Esp32 clk.png]] | ||

| + | CPU_CLK 由RTC_CNTL_SOC_CLK_SEL 来选择时钟源,160MHz~8MHz | ||

| + | EMAC: APB_CLK | ||

2020年2月16日 (日) 17:58的最后版本

2x Xtensa LX6 CPU.

两个CPU 的名称分别是“PRO_CPU”和“APP_CPU”。PRO 代表“protocol(协议)”,APP 代表“application

(应用)”。在大多数情况下,两个CPU 的功能是相同的。

| start | end | size | usage | on-chip | usage |

|---|---|---|---|---|---|

| 0x0000_0000 | 0x3F3F_FFFF | no use | |||

| 0x3F40_0000 | 0x3F7F_FFFF | 4M | data | ext | Flash |

| 0x3F80_0000 | 0x3FCBF_FFFF | 4M | data | ext | SRAM |

| 0x3FC0_0000 | 0x3FEF_FFFF | 3M | no use | ||

| 0x3FF0_0000 | 0x3FF7_FFFF | 512K | data | I/O | |

| 0x3FF8_0000 | 0x3FF8_1FFF | 8K | data | internal | RTC Fast Memory (PRO_CPU only) |

| 0x3FF8_2000 | 0x3FF8_FFFF | 56K | no use | ||

| 0x3FF9_0000 | 0x3FF9_FFFF | 64K | data | Internal | ROM 1 |

| 0x3FFA_0000 | 0x3FFA_DFFF | 56K | no use | ||

| 0x3FFA_E000 | 0x3FFD_FFFF | 200K | data | Internal | SRAM 2 (DMA) |

| 0x3FFE_0000 | 0x3FFF_FFFF | 128K | data | Internal | SRAM 1 (DMA) |

| 0x4000_0000 | 0x4005_FFFF | 384K | code | Internal | ROM 0 |

| 0x4006_0000 | 0x4006_FFFF | 64K | no use | ||

| 0x4007_0000 | 0x400A_FFFF | 192K | code | internal | SRAM 0 (64KB cache) |

| 0x400A_0000 | 0x400A_FFFF | 128K | code | internal | SRAM 1 |

| 0x400C_0000 | 0x400C_1FFF | 8K | code | internal | RTC fast Memory (PRO_CPU only) |

| 0x400C_2000 | 0x40BF_FFFF | 11512K | code | ext | flash |

| 0x40C0_0000 | 0x4FFF_FFFF | 244M | no use | ||

| 0x5000_0000 | 0x5000_1FFF | 8K | code/data | internal | RTC Slow Memory |

| 0x5000_2000 | 0xFFFF_FFFF | no use |

DMA:

UART0,1,2 SPI1,2,3 I2S0,1 SDIO slave, SDMMC EMAC BT WIFI

Peripharels: 41 device

control registers 0x3FF0_0000~ 0x3FF7_FFFF, each device use 4KB space. 系统中有两个PID Controller 分别服务于PRO_CPU 和APP_CPU。 CPU 不能访问对方的PID Controller

Interrupt:

71 external sources: 71 个外部中断源中有67 个可以分配给两个CPU。其余的4 个外部中断源只能分配给特定的CPU,每个CPU 2 个。

26 interrupt source for each core.

each CPU has 32x interrupt, include 26x external interrupt.

internal interrupt: (6/7/11/15/16/29)

timer0/1/2, software,

Reset:

COU reset: 只复位CPU 的所有寄存器。(CPU) Core reset: 除了RTC,会把整个digital 的寄存器全部复位,包括CPU、所有外设和数字GPIO。 (CPU+WIFI+BT+PERI+Digital GPIO) system rest: 会复位整个芯片所有的寄存器,包括RTC (PMG+Sensor+ULP+RTC GPIO)。

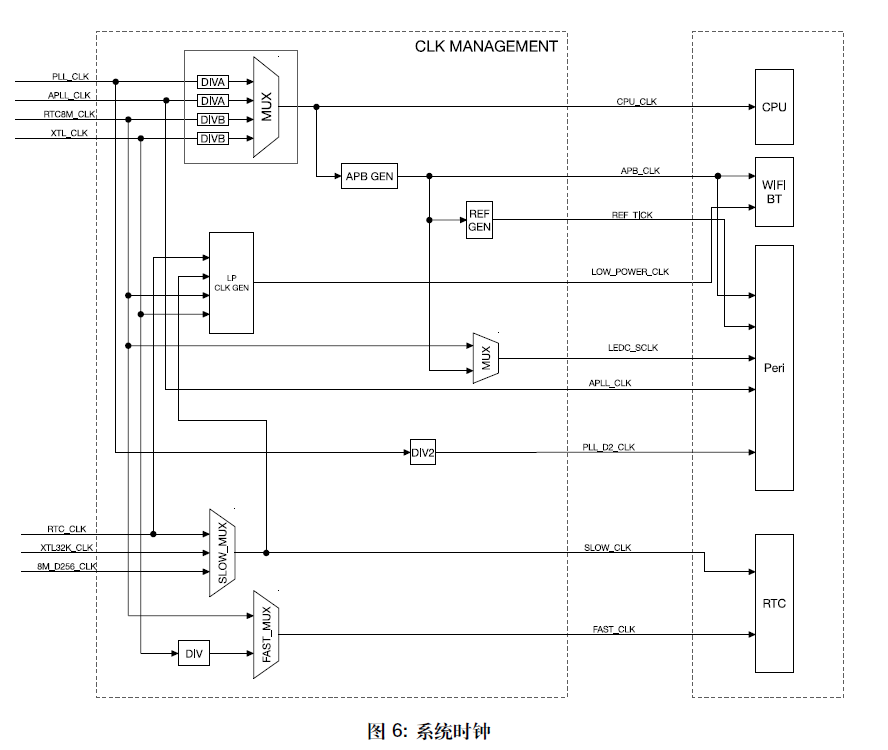

Clock sources:

• 快速时钟 – PLL_CLK,320 MHz 内部PLL 时钟 – XTL_CLK,2 ~ 40 MHz 外部晶振时钟 • 低功耗慢速时钟 – XTL32K_CLK,32 KHz 外部晶振时钟 – RTC8M_CLK,8 MHz 内部时钟,频率可调 – RTC8M_D256_CLK 由RTC8M_CLK 256 分频所得,频率为(RTC8M_CLK 256)。当RTC8M_CLK 的初始频率为8 MHz 时,该时钟以31.250 KHz 的频率运行。 – RTC_CLK,150 KHz 内部低功耗时钟,频率可调 • 音频时钟 – APLL_CLK,16 ~ 128 MHz 内部Audio PLL 时钟

CPU_CLK 由RTC_CNTL_SOC_CLK_SEL 来选择时钟源,160MHz~8MHz EMAC: APB_CLK